一般来说,在DDR硬件电路设计过程中,DDR电源设计中存在不合理的部分。下面简要介绍一下DDR电源:DDR电源可以分为三类:(1)主电源VDD和VDDQ main电源要求是VDDQ = VDD,VDDQ是IO缓冲器的电源,而VDD是但通常使用时,VDDQ和VDD合并为一个电源。

一些芯片还具有VDDL,该VDDL为DLL供电,并且可以使用与VDD相同的电源。在设计电源时,必须考虑电压和电流是否满足要求,电源的上电顺序,电源的上电时间以及单调性。

电源电压要求通常在±5%以内。需要根据使用的不同芯片和芯片数量来计算电流。

由于DDR的电流通常比较大,因此在PCB设计期间如果在引脚上放置完整的电源平面,并且在电源入口处增加电容器的能量存储,并在每个引脚上增加一个电容,则这是最理想的状态。用一个10nF〜100nF的小电容进行滤波。

(2)基准电源VrefVref是基准电压,要求其准确且恒定,并且用作判断信号的高电平和低电平的基础。所有DDR信号实际上都是相对于Vref的差分信号,因此它们也是差分信号。

有关更多详细信息,请参阅``高速电路设计实践''中有关DDR的章节。要求参考电源Vref跟随VDDQ,并且Vref = VDDQ / 2,因此它可以由电源芯片提供,也可以由电阻分压器获得。

由于Vref电流通常很小,约为几mA到几十mA,因此电阻分压器方法节省了成本,并且布局更灵活。它靠近Vref引脚放置,并紧随其后。

VDDQ电压,因此建议使用此方法。需要注意的是,用于分压器的电阻可以为100〜10K,需要精度为1%的电阻。

Vref参考电压的每个引脚都需要添加一个10nF的电容器进行滤波,最好将一个电容器与每个分压电阻并联。 Vref分为Vrefca和Vrefdq:Vrefca电源用于控制,命令和地址的参考电压:必须始终保持Vrefca(包括自刷新),以使设备正常工作Vrefdq电源数据的参考电压:Vrefdq必须始终保持次(不包括自刷新),以确保设备正常运行。

以下是FSL i.MX6设计的屏幕截图:从V REF到其他走线的间距至少保持20-25 mil;如有可能,将VREF与相邻的接地走线隔离。 (nxp-fsl设计指南)(3)VTT(跟踪终端电压)VTT用于匹配,用于上拉和下拉电阻器的电源,具有大电流,大波动和大噪声。

VTT是由匹配电阻VTT = VDDQ / 2上拉的电源。在DDR设计中,取决于拓扑,某些设计不使用VTT,例如当控制器具有较少的DDR设备时。

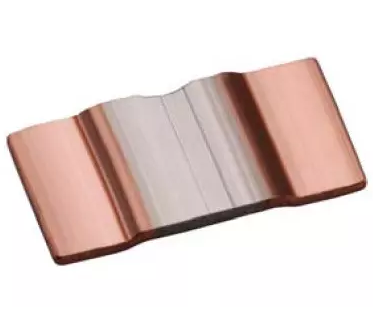

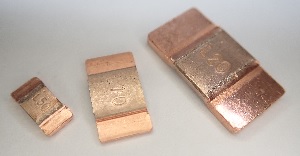

如果使用VTT,则VTT的电流要求相对较大,因此必须使用铜布线。 VTT要求电源可以提供电流和灌电流(灌电流)。

在正常情况下,您可以使用专门为DDR设计的电源芯片来生成满足要求的VTT(我在使用过程中使用了简单的线性稳压器,但没有发现问题,仍然不建议使用此方法!)。此外,通常在靠近VTT的每个电阻旁边放置一个10nF〜100nF的电容器,并且需要一个大的uF电容器来存储整个VTT电路上的能量。

通常,DDR数据线具有一驱动器一的拓扑结构,并且DDR2和DDR3都具有用于匹配的ODT,因此无需拉动VTT进行匹配即可获得更好的信号质量。但是,如果地址和控制信号线是多负载的,将有多个驱动器,并且内部没有ODT,并且其拓扑结构是T点结构,因此通常需要使用VTT来提高信号质量匹配控件。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: momo@jepsun.com

产品经理: 李经理

QQ: 2215069954

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- 磁性感应接近开关SMC D-C73:高效稳定的自动化控制选择 磁性感应接近开关SMC D-C73是一种高效、非接触式的检测设备,广泛应用于自动化控制领域。这种开关能够检测到特定类型的磁场变化,并据此触发开关动作,无需物理接触即可完成信号的传输与处理,因此在提高设备运行效率的...

- 施耐德LC1-D系列交流接触器:可靠性能与优质服务 施耐德电气作为全球能效管理和自动化领域的专家,在电气领域有着卓越的表现。其产品线中的LC1-D系列交流接触器是工业控制领域中不可或缺的一部分。其中,LC1-D25型号接触器以其高质量和可靠性能著称,适用于多种工业场景...

- 冲击接地电阻值不得大于多少 避雷器、电缆金属外皮、钢管和绝缘子铁脚、金具等应连在一起接地,其冲击接地电阻不宜大于10Ω。 第12.7.2条:输送危险物质的各种室外架空管,应每隔20~25米接地一次,每处冲击接地电阻不应大于10Ω。 第12.7.3条:危险区域应...

- 聚鼎PH-D瞬态抑制二极管插件TVS管应用及选型指南 在电子设备中,瞬态电压抑制二极管(Transient Voltage Suppressor,简称TVS管)作为关键的保护元件,在面对瞬态过电压时能够迅速响应,有效地保护电路中的敏感器件免受损害。聚鼎科技(PU Diode)作为国内知名的半导体制造商,其...

- 防雷冲击接地电阻值不得大于多少 标准接地电阻规范要求: 1、独立防雷接地电阻≤10Ω; 2、独立安全保护接地电阻≤4Ω; 3、独立交流工作接地电阻≤4Ω; 4、独立直流工作接地电阻≤4Ω; 5、防静电接地电阻一般要求≤10Ω。&am...

- 普通电阻作为吸收负载选型原则,假设吸收功率300mW 普通电阻作为吸收负载时,选型原则如下:1、根据负载功率选择电阻值在选择普通电阻时,需要根据负载功率来选择合适的电阻值。通常情况下,吸收负载需要选择大于或等于负载功率的电阻值。例如,如果负载功率为300mW,则...

- 水流开关:保障设备安全运行的关键部件 水流开关是工业自动化管理领域中的一种重要控制元件。在各种水冷系统、空调系统、供暖系统及其它需要监测水流状态的设备中,水流开关扮演着不可或缺的角色。它主要用于检测管道中的水流是否正常流动,一旦发现水流异...

- 高纹波GQ系列电源设计与应用详解 在现代电子设备中,电源作为核心组件之一,其性能直接影响到系统的稳定性和可靠性。高纹波GQ系列电源因其独特的性能特点,在众多应用场景中脱颖而出。本文将围绕高纹波GQ系列电源的设计理念、技术特点及其应用领域进行...

- 在通过滤波器设计中考虑电阻电容值 只有非常狭窄的电气输入功率范围才能触发固态继电器,因此在继电器输入端必须有一个电噪声屏蔽罩,以防止发生任何错误或故障情况。电阻电容(RC)网络是吸收这种脉冲噪声的一种简单有效的方法。尽管它是普通的RC低通滤...

- 数显压力开关:现代工业自动化控制的重要组成部分 数显压力开关是一种现代化的压力控制设备,它结合了传统机械式压力开关的实用性与数字技术的精准性。以成瑞品牌的数显压力开关为例,这类产品通常具备高精度的压力测量功能,能够实时显示当前系统内的压力值,并在达...

- SGM2054设备低成本低外部终端调节器 SGM2054设备是一个是一个宿和源DD(双倍数据速率)终端调节器。它专门为低成本和低外部部件数量的系统设计。其他功能包括逻辑控制关机模式、远程感应和软启动功能,可减少浪涌电流确保为DDR2、DDR3、低功耗DDR3、DDR3L、DDR4和...

- BHZ51-10、25、60/380矿用隔爆型转换开关:专为煤矿安全设计的高性能电气设备 BHZ51-10、25、60/380矿用隔爆型转换开关是一种专为煤矿井下等具有爆炸性气体混合物环境中使用的电气设备。该型号的转换开关采用先进的设计理念和制造工艺,确保其在恶劣环境下也能稳定运行。其主要功能是用于接通或断开电...

- 分立组件功能数组在系统设计中的应用与优势 在现代系统的构建中,分立组件功能数组的应用日益广泛,这不仅是因为它能够提高系统的灵活性和可维护性,还因为它能够在复杂的系统环境中实现更高效的资源分配和管理。分立组件功能数组指的是将系统功能按照特定规则...

- 万用表测得电阻阻值为0的原因及解决办法 使用万用表测量电阻时,如果显示的阻值为0,这通常意味着两种情况。第一种可能是电阻器已经短路,即内部导体直接连接了两端点,没有提供任何阻抗,这种情况下的电阻器已经失效,无法正常使用。第二种可能是测量方法或...

- 关于电阻量程40欧姆的测量设备及其应用 在电子测量领域中,对于特定量程如40欧姆的电阻,需要选用合适的测量工具以确保准确度。通常,万用表或专门的电阻测量仪器能够提供这样的量程。这些设备通过不同的方法来测量电阻值,包括但不限于电流-电压法,即根据...

- 用于测试电源的负载类型 测试电源时,有两个不同的负载可用于此过程。有台式电子负载测试仪,例如上面显示的B&K Precision部件,可以拨入不同的负载大小以适应在许多不同设备上进行的测试。电子负载测试仪的另一个好处是它们具有内置保护,而标...

- DC-DC外部功率级应用与优势分析 在现代电力电子系统中,DC-DC转换器扮演着至关重要的角色,它们被广泛应用于各种设备和系统中,从消费电子产品到工业控制系统,再到可再生能源系统。DC-DC外部功率级作为DC-DC转换器的一个重要组成部分,其作用在于提高系...

- TVS管可以用于多相电源系统吗? 可以,TVS管可以用于多相电源系统。因为TVS管可以用于交流电路,而多相电源系统通常是交流电路。此外,TVS管可以保护变压器以后的所有电路元件,因此可以在多相电源系统中起到保护作用。...

- 生产数字式压力开关:从设计到应用 生产数字式压力开关是一项结合了精密机械制造与现代电子技术的工业活动。数字式压力开关是一种用于自动控制系统中的重要部件,它可以将液体或气体的压力转换为电信号,并根据预设值进行控制操作。这种设备广泛应用于...

- 电容触摸开关触点设计 电容式感应触摸开关触摸开关按开关原理分类有电阻式触摸开关和电容式触摸开关,在多种技术中,电容式触摸感应技术已经成为触摸感应技术的主流,在按键方案上,能为产品带来整体的外观档次提升。电容式感应触摸开关可...